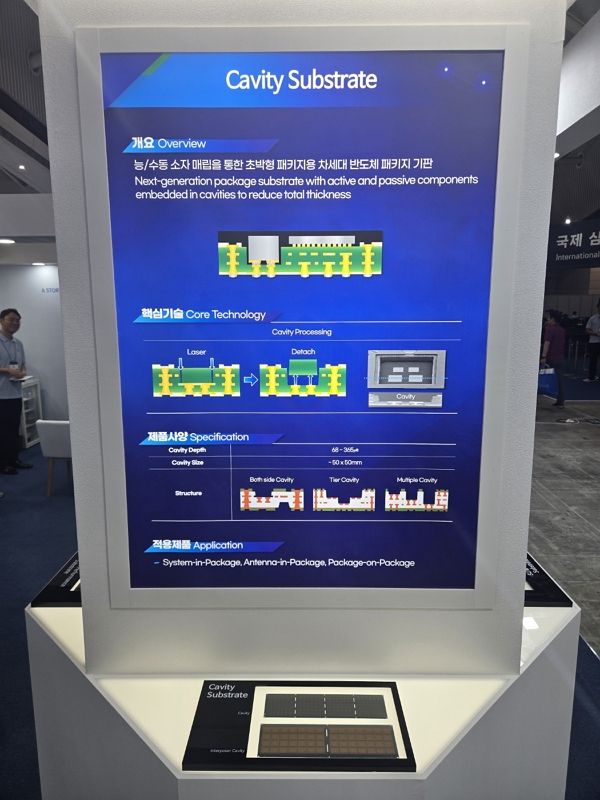

PoP·AiP 패키지 적용 가능한 캐비티 기판 개발

[시사저널e=고명훈 기자] 인쇄회로기판(PCB) 전문업체 심텍이 초박형 패키지용 차세대 반도체 기판으로 지목되는 캐비티(Cavity) 서브스트레이트(기판) 기술을 확보했다. 심텍은 얇은 기판으로 스마트폰 패키지 시장을 공략한다.

11일 반도체 기판업계에 따르면 심텍은 패키지온패키지(PoP), 안테나인패키지(AiP) 등에 적용할 수 있는 캐피티 기판 개발을 완료했다. 현재 거래선과 협력해 평가중이다.

캐비티는 레이저로 기판 일부를 잘라 빈공간을 만들고, 그 공간의 모양대로 소자를 매립해 패키징하는 기술이다. 두께를 줄일 수 있단 장점 때문에 작은 폼팩터 안에 칩 사이즈를 최소화해야 하는 모바일 패키징 분야에서 해당 기술에 대한 관심이 높은 것으로 전해진다.

PoP는 3차원 적층을 위한 패키징 기술로, 주로 모바일 제품에 많이 활용된다. 바닥면에 플립칩 볼그리드어레이(FCBGA)가 깔려 있고, 그 위에 또 다른 FCBGA와 인터포저, 메모리 순으로 적층된 형태다.

심텍은 해당 패키지 중간에서 기판과 다이(die)를 연결해주는 인터포저 부품을 캐비티 형태로 만드는 기술을 개발했다. 회사는 이와 함께 5G 스마트폰 출시가 확대되면서 중요성이 높아진 AiP에도 패키지 제품의 두께를 감축할 수 있는 AiP 캐비티 개발을 완료했다.

심텍 관계자는 “기존에 있던 인터포저를 캐비티 형태로 파서 만들어 놓으면 전체 높이를 낮추는 데 유리해진다”고 설명했다.

그러면서 “PoP, 안테나 패키지쪽에서 캐비티에 대한 관심이 높고, 인터페이스쪽에서도 문의가 들어오고 있다”며 “스마트폰에서 소켓(네트워크상에서 두 지점 간 통신을 위한 인터페이스)을 아예 배제하겠다는 개념으로 해당 솔루션에 관심을 갖는 경우가 있다”고 말했다.

캐비티 기판은 반도체 패키징의 다기능·고집적화 트렌드에 대응하기 위한 핵심 기술로 지목된다. 심텍 외에도 삼성전기, 대덕전자 등이 기술 개발에 나섰다.

심텍 관계자는 “캐비티 기판이 경쟁사 제품 대비 소재에 대한 제한성이 없어 유연하게 대응할 수 있다”고 설명했다.

심텍 관계자는 “특수하게 레이저로 전체 영역만큼 자르는 게 아니라 겉부분만 잘라서 떼내고 바닥면을 식각하는 형태로, 가격이나 시간 면에서 더 효율적”이라며 “바깥쪽만 잘라내서 떼어내는 방식이라 소재에 대한 제한성 없이 다양한 소재 적용이 가능하단 이점이 있다”고 말했다.

이어 “양면, 단면에도 캐비티를 만들 수 있고, 멀티플(Multiple), 티어(Tier), 보스사이드(Both side) 등 어떤 구조로도 구현해 내 요청을 만족시킬 수 있다”며, “현재 고객사 몇 곳에서 평가를 계속 진행 중”이라고 부연했다.

심텍은 모바일용 패키지 시장 외에도 고성능컴퓨팅(HPC)을 공략하기 위한 유리기판 개발에도 속도를 내고 있다.

회사 관계자는 “유리기판 핵심 기술 관련해서 현재 과제를 진행 중인데 어느 정도 마무리되면 기존 플립칩과 같은 고밀도 기판의 코어층에 적용해서 실제 제품을 평가해봐야 할 것”이라고 말했다.

이어 “유리 소재 기판이 아직 깨짐이나 검정 핸들링 부분에서 문제점이 많다 보니 앞으로 약품을 사용하는 등 처리 방법을 얻기까지 좀 더 시간이 필요할 것”이라고 덧붙였다.