“HBM 제조에 적용하려면 MI 기술로 공정 최적화 작업 필요”

[시사저널e=고명훈 기자] SK하이닉스가 반도체 계측·검사(MI) 솔루션 개선을 위한 중요한 플랫폼 기술로 하이브리드 본딩을 지목했다. MI는 반도체 제조공정 전·후 사이사이에 들어가 레이어(Layer) 등의 결함을 점검하는 것으로, 최근 제조 기술이 고도화되고 장비 대수도 급격히 늘면서 수율과 품질을 개선하기 위한 필수 단계로 꼽힌다.

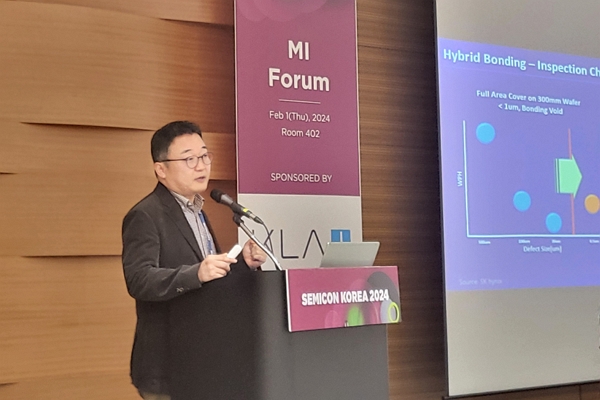

강지호 SK하이닉스 웨이퍼본딩(WF) 담당(부사장)은 1일 코엑스에서 열린 ‘세미콘코리아 2023’ MI 포럼에서 “MI 기술을 확보하기 위해 학계, 산업계 및 장비 파트너사들의 노력이 결부돼야 한다”며 “여기에서 하이브리드 본딩은 최신 MI 기술을 제공하는 게임체인저이자 핵심 플랫폼 기술이 될 것”이라고 말했다.

하이브리드 본딩은 서로 다른 두 개의 칩셋을 이어 붙인 후 이를 실리콘 관통전극(TSV)으로 연결해 접착하는 방식으로, 메모리 반도체를 고단층으로 쌓아서 제조할 때 유용하게 적용할 수 있는 기술로 주목받는다. 기존에 칩셋을 붙일 때는 그 사이에 공 모양의 전도성 돌기인 범프를 여러 개 둬야 했는데, 하이브리드 본딩은 범프 없이도 다이렉트로 붙일 수 있어 전체 패키징 제품 크기를 줄일 수 있다는 장점이 있다.

SK하이닉스는 하이브리드 본딩의 이런 기술적 장점을 살려 3D D램과 400단 이상의 낸드플래시에 적용해 개발 중인 것으로 전해졌다. 최근 AI향 메모리로 주목받는 고대역폭메모리(HBM)에도 D램을 12단 이상 적층한 제품부터 하이브리드 본딩을 채택할 계획이다.

강 부사장은 “오늘날 하나의 웨이퍼로 모든 것을 만드는 것은 매우 어렵기 때문에 기능별로 서로 분리된 장치들을 결합하는 것이 필요하다”며 “따라서 인공지능(AI)이 요구하는 기술과 데이터 처리능력을 충족하기 위해 결국 웨이퍼레벨과 칩레벨에서 하이브리드 본딩이라는 플랫폼 기술을 거쳐야 한다고 생각한다”고 말했다.

SK하이닉스는 HBM 제조에 하이브리드 본딩을 활용하기 위해 공정 최적화 작업이 필요하다고 제시했다. MI 기술의 발전이 이런 최적화 작업의 필수 요소라고 강조했다.

강 부사장은 “본딩 공정 개선을 위해 두 웨이퍼가 같은 구리 계면이라 해도 접합 계면의 평탄도와 워피지(휨현상) 제어 등 수준이 어느 정도인지를 고려해야 하고, 본딩 전처리나 어닐링(웨이퍼에 상처가 아물도록 온도 변화를 주는 공정)으로 접합 강도가 달라지면 제조 쓰루풋(처리량)도 달라지기 때문에 탑과 바텀 웨이퍼를 정확하게 정렬해야 한다”며 “마지막으로, 8단과 12단 등 단수에 따라 웨이퍼의 양, 개수, 스탬프가 얼마나 돼야 하는지를 검토하는 것도 개발 능력을 높이기 위한 핵심 분야”라고 덧붙였다.

그는 “웨이퍼를 접합했을 때 빈틈이 생기지 않도록 웨이퍼상에 있는 돌출 및 침식 부분을 제어해야 하므로, 본딩 공정 전에 표면 상태를 검사하는 것이 매우 중요하다”며 “원자현미경(AFM)이 금속 패터닝 등 분석에 매우 적합한 해결책이란 건 알고 있지만, HBM에 대한 쓰루풋(처리율)을 향상시키는 것이 필요하다”고 설명했다.

반도체 칩을 수직으로 연속되게 쌓아 올릴 때 각 층이 얼마나 정확한 위치에서 빗나가지 않고 쌓을 수 있는지 측정도 중요하다고 강조했다. 강 부사장은 “칩 정렬의 정확도를 측정하는 것은 기존의 측정 방식과는 달리, 적외선이 두꺼운 실리콘을 관통해 본딩 웨이퍼 사이의 오버레이 정렬을 측정하는 것으로, 이는 MI 기술의 또 다른 중요한 영역이 될 것”이라고 말했다.