2.5D 패키징도 한계···2.1D 기술 개발 전념

미세회로·임베딩 솔루션 고도화 가속

[시사저널e=고명훈 기자] 삼성전기가 인공지능(AI) 서버 시장을 겨냥해 반도체와 메인보드 연결 기술에 집중한다. AI용 서버기판 시장은 서버 시장 위축에도 당분간 공급부족이 예상된다.

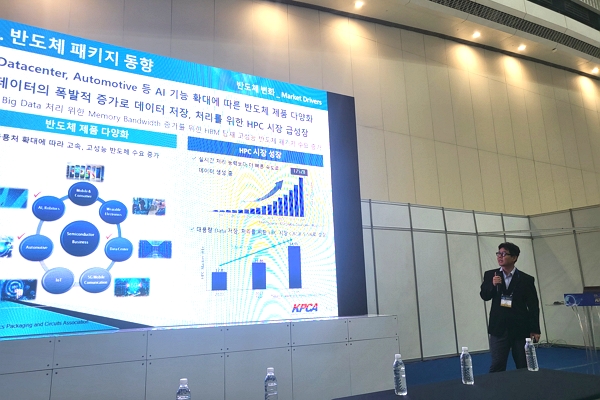

김용훈 삼성전기 패키지마케팅 그룹장은 6일 인천 송도컨벤시아에서 열린 ‘국제 PCB 및 반도체패키징산업전(KPCA show 2023)’ 심포지엄에서 “(AI칩 내) HBM 탑재 수가 10개 이상 넘어가면 미세회로 기판 크기가 커질 수밖에 없는데, 이렇게 되면 웨이퍼 한장당 생산할 수 있는 제품 수가 줄어든다”며 “종합반도체기업(IDM)은 물론 파운드리, 후공정(OSAT), 기판업체 모두 각 사 고유의 어드밴스드 패키징 기술을 개발 중”이라고 설명했다.

김 그룹장은 패키지 기판에서 휨 현상(Warpage)을 제어할 수 있는 부품 실장 능력 개선에 주력하고 있다고 전했다. 대면적 로직 다이(Die)에서 HBM, 로직, 다이와 다이를 효율적으로 연결하려면 2.5D를 넘어 2.3D, 2.1D 등의 패키징 솔루션이 필요하다. 이중 2.5D는 실리콘 인터포저라는 별도의 회로 기판 위에 로직 다이가 배치된 구조로, 대만의 TSMC가 처음 선보인 이후 현재 AI 칩과 HBM 연결에 가장 많이 쓰이는 첨단 패키징 기술로 자리 잡았다.

김 그룹장은 HBM 탑재 수가 향후 10개~12개로 증가하게 되면 2.5D 구조에서도 한계가 발생할 것이라고 지적했다. 2.3D는 2.5D에서 실리콘 인터포저 대신 브릿지 또는 재배선(RDL) 인터포저가 들어가는 구조이며, 2.1D는 실리콘 브린지가 기판에 내장됐거나 RDL이 기판 위에 있는 형태다. 삼성전기는 2.1D가 기판 기술에 큰 영향을 받는 패키징 기술이라며 현재 여기에 집중하고 있다.

김 그룹장은 “내장형(임베드) RDL과 2.1D가 앞으로 대세가 될 것으로 보고 있고 2025년 말이나 2026년 정도 되면 관련 시장이 커질 것으로 생각된다”고 말했다.

아울러, 삼성전기는 반도체 입출력(I/O) 단자 수 증가 추세에 따라 미세회로 개발도 진행 중이다. 김 그룹장은 “HBM이나 칩 투 칩을 연결하는 I/O 수가 이제는 수십개가 아니고 수천개 수준으로 증가했다”며 “반드시 미세회로가 필요하고 미세 회로용 노광 및 에칭 기술, 신호 손실 최소화를 위한 구리(CU) 표면 조도 저감 기술을 개발하고 있다”고 설명했다.

전원 무결성(Pi) 개선을 위한 임베딩 솔루션 요청도 지속 증가했다. 임베딩은 기판 내 수동소자(저항기)를 내장하는 기술로, 삼성전기는 해당 기술 적용을 통해 신호 경로를 단축함으로써 Pi 성능을 30~50% 향상하는 데 성공했다고 밝혔다.이외에도 삼성전기는 고밀도의 신규 절연재 개발도 필수라고 강조했다.

한편, 엔비디아를 시작으로 빅테크 기업들의 AI 서버에 대한 투자가 기하급수적으로 증가하면서 AI 서버용 반도체 패키지 기판의 공급은 당분간 수요를 따라가지 못할 것으로 관측된다.

이날 삼성전기 관계자는 “같은 서버용이라도 엔비디아에서 하는 AI 반도체향 HBM쪽은 계속 공급 부족 현상이 지속될 것으로 본다”라며, “반도체 기판업체들은 각자 로드맵을 갖고 이런 수요에 대응하기 위한 연구개발(R&D)을 같이 하고 있으며, 하이엔드 패키징 기판인 FC-BGA에서 국내 유일하게 서버용 제품을 양산하고 있다”고 강조했다.